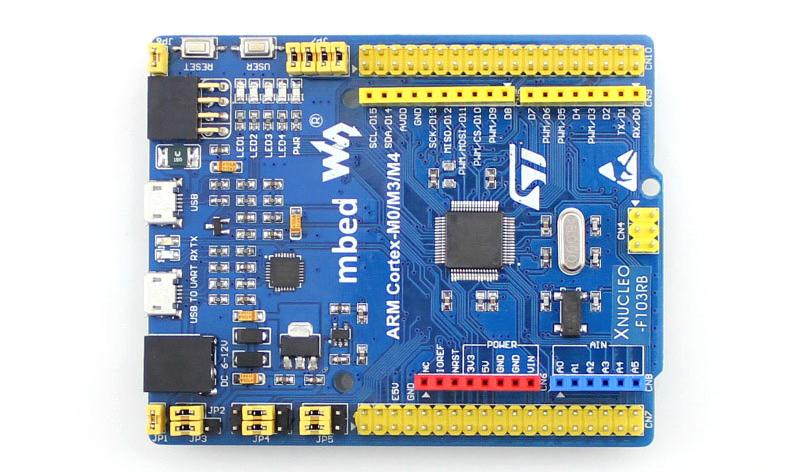

半导体芯片封装是指利用膜技术和微加工技术将芯片等元件铺设、固定、连接在框架或基板上,引出接线端子,用塑料绝缘介质密封固定,形成整体三维结构的过程。这个概念是一个狭义的包装定义。更广义的封装是指封装工程,将封装与基板连接固定,组装成一个完整的系统或电子设备,并保证整个系统的综合性能。结合前面两个定义构成了一个广义的包装概念。

半导体封装用途1、保护

半导体制造车间对生产条件的控制非常严格,比如恒温(2303 * C)、恒湿(5010%)、严格的粉尘粒径控制(一般在1K到10K之间)、严格的静电防护措施等。只有在这样严格的环境控制下,裸封装芯片才不会失效。但是,我们所处的周边环境是完全不可能满足这个条件的。低温可能是-40,高温可能是60*C,湿度可能达到100%。如果是汽车产品,其工作温度可能高达120^C或更高。为了保护芯片,我们需要对其进行封装。

2、支持

支架有两个作用:一是支撑芯片,固定芯片方便电路连接;另一种是在封装完成后形成一定的形状来支撑整个器件,使整个器件不容易损坏。

3、连接

连接的作用是将芯片的电极与外部电路连接起来。引脚用于与外部电路通信,金线连接引脚与芯片的电路。载物台用于承载芯片,环氧胶用于将芯片粘在载物台上,引脚用于支撑整个器件,塑封起到固定和保护的作用。

4、可靠性

任何包装都需要形成一定的可靠性,这是整个包装过程中最重要的措施。原来的芯片离开特定的生活环境就会损坏,需要进行封装。芯片的工作寿命主要取决于封装材料和封装工艺的选择。

半导体芯片封装工艺流程

1、封装工艺一般可分为两部分,塑封前的工艺步骤成为前工序,成型后的工艺步骤成为后工序。

2、芯片封装技术基本工艺流程:硅片减薄、硅片切割、芯片贴装、芯片互连成型技术、去毛刺、切筋、成型、焊接、打码等

3、硅片背面减薄技术主要包括研磨、磨削、化学机械抛光、干法抛光、电化学腐蚀、湿法腐蚀、等离子体增强化学腐蚀、大气压等离子体腐蚀等。

4、先划线后减薄:在背磨前将硅片正面切割到一定深度,然后进行背磨。

5、减薄划线:减薄前,用机械或化学方法切割缺口,然后用研磨的方法减薄到一定的厚度。之后,利用ADPE刻蚀技术去除剩余的加工量,实现裸芯片的自动分离。

6、芯片贴装有四种方式:共晶键合、锡焊键合、导电胶键合、玻璃胶键合。

共晶键合法:利用金硅合金(一般为69%Au,31% Si),363度的共晶熔融反应使ic芯片键合固定。

为了获得最佳的共晶安装方法,ic芯片的背面通常镀有金薄膜,或者在基板的芯片载体上植入预芯片。

芯片互连的常见方法包括引线接合、自动接合(TAB)和倒装芯片接合。

引线接合技术包括超声波接合、热压接合和热超声波接合。

10、TAB TAB关键技术:1芯片凸点制造技术2 TAB卷带制造技术3卷带引线与芯片凸点的内引线焊接与外引线焊接。

11、凸点芯片制造技术,凸点形成技术:蒸发/溅射法,电镀法,球放置和模板印刷,焊料凸点,化学镀法,球凸点法,激光法。

12、塑料封装成型技术,1传递成型技术,2注塑成型技术,3预成型技术,但最重要的技术是传递成型技术,一般采用热固性聚合物。

13、薄型芯片有以下优点1、薄型芯片更有利于散热;2、减小芯片的封装体积;3、提高机械性能,硅片薄,其柔韧性越好,外部冲击产生的应力越小;4、晶圆厚度越薄,元件之间的连线越短,元件的导通电阻越低,信号延迟时间越短,从而实现更高的性能;5、减薄后减少划线量和切割可以减少划线量和芯片破损的发生率。

14、波峰焊:波峰焊的工艺流程包括在一个焊料波峰上涂助焊剂、预热、通过PCB。助焊剂在表面张力和毛细现象的共同作用下被带到PCB和元件引脚上,形成焊点。

波峰焊是熔化的液态焊料借助于泵在焊料池的液面上形成特定形状的焊料波,将带有元件的PCB板放置在输送链上,以特定的角度和一定的进入深度穿过焊料波峰,实现焊点的焊接。

回流焊(Reflow soldering):是预先将适量、适当形式的焊料涂在PCB焊接位置,然后贴合表面贴装元件,再将预先分布在PCB焊盘上的焊膏重新熔化,实现表面贴装元件的焊接端子或引脚与PCB焊盘之间的机械和电气连接的一组或逐点焊接工艺。

15、引线键合(WB):将细金属线或条依次键合在芯片和引线框架或封装基板的焊盘上,形成电路互连。引线接合技术包括超声波接合、热压接合和热超声波接合。

自动卷带(TAB):用带有引线图案的金属箔线将芯片焊盘与电子封装外壳的I/O或基板上的金属布线焊盘连接起来的工艺过程。

倒装焊(FCB):芯片朝下,芯片和基板的焊盘直接连接的一种方法。

16、芯片互连:将芯片焊盘与电子封装外壳的I/O或基板上的金属布线焊盘连接。只有实现芯片与封装结构之间的电路连接,才能发挥现有的功能。