FPGA开发流程概述开始学习FPGA。如果想尽快入门FPGA开发,先来了解一下FPGA的开发流程。

1、模块划分需求分析

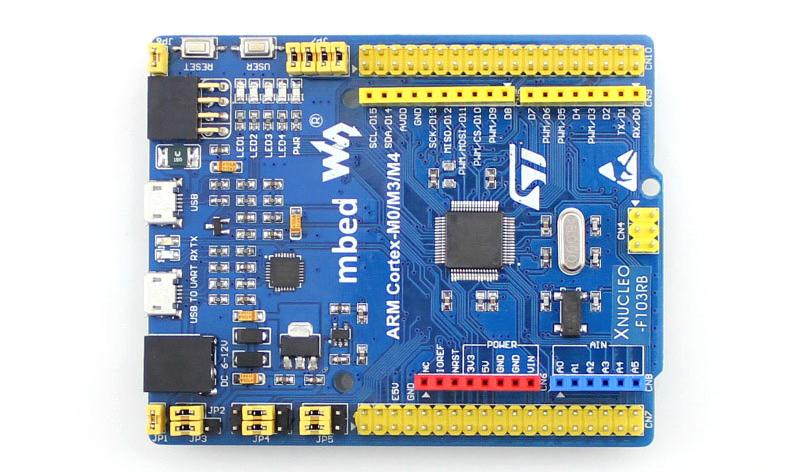

需求描述文件;器件选择(逻辑资源、功耗、IO数、封装等。);配置电路考虑因素;开发工具的选择;电路板的可扩展性考虑;在线调试和板级调试注意事项;模块化设计。

2、全面优化的设计输入

设计输入:原理图,Verilog,VHDL。

综合:是指将一个较高层次的电路描述转化为一个较低层次的电路描述。即把设计代码转换成由与门、非门、RAM、触发器等基本逻辑单元互连而成的网表。综合工具可以使用Synplicity的Synplify实现,也可以使用设备厂商提供的开发工具实现(实现是指:翻译、映射、布局和布线)。

代码设计完成后,最好先用开发工具检查语法,再进行功能模拟,这里的模拟不涉及时间延迟。ModelTech的ModelSim是第一个仿真工具,ISE的Quartus 2也可以进行简单的仿真。

3、实现时序收敛

实现:

翻译-将合成结果转换成所选设备的底层模块和硬件原语;

映射-将翻译结果映射到特定设备;

布局布线——根据用户的设计约束进行布局布线,完成FPGA内部逻辑的连接;

时序收敛:(设计关键,时序收敛必须满足)

工具的最红布局满足设计者输入的时序约束要求。

4、模拟至电路板调试

主要验证采用仿真和板级调试。FPGA板级调试的一个大问题是同步观察接口信号数量有限,很难观察到内部信号节点的状态。如果纯粹是板级调试,会消耗太多的人力物力。

FPGA仿真很重要,但和其他软件开发中的仿真概念不太一样。在时序电路中,逻辑变化的每一步都是由时间的结束边沿触发的,所以在调试时通过控制时钟频率来达到单步的效果显然是不可能的。

一般开发团队不会严格的把三个模拟都进行,一般会做行为模拟和时序模拟。当我们能熟练编写综合代码时,只需要做功能模拟,时序模拟一般不做。我们会花时间做深入细致的时序约束,通过时序报表分析解决时序问题。

FPGA的调试方法有很多种,使用示波器和逻辑分析仪的调试方法是最常用的。如ISE和Quartus的Chipscope2、 signal tap 2。练习的时候可以用Quartus 2。

关于Quaryus 2的开发过程,请参考Help-PDF _ Tutorials-Verilog HDL用户:

这里不详细介绍Quartus 2项目的建立、使用和编译,但是你要了解任务窗口的编译步骤:

编制设计使用说明

分析综合-分析综合

钳工(放置路线)-适应(布局)

汇编程序(生成编程文件)——生成相应的文件用于编程和下载配置,一般为位数据流和sof/pof格式。

TimeQuest时序分析-时序分析

向Quartus 2支持的第三方提供网表。

程序设计器(开放式编程器)-配置