我们将介绍:

DDR x4 x8 x16芯片宽度

DDR银行等级

DDR银行集团

DDR预取

DDR页面大小

DDRRow缓冲区

DDR存储体交错

DDR单元命令序列

DDR x4 x8 x16

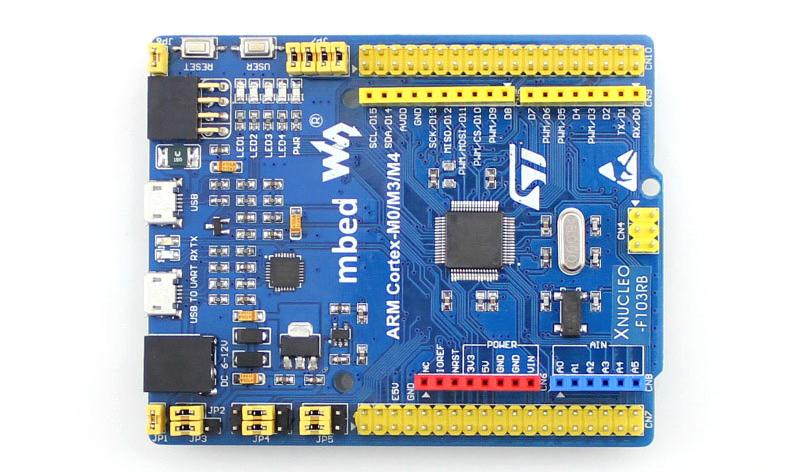

X4xx8x16指的是上图中黑芯片输出的位宽,正常的DDR总线宽度需要64位,所以

芯片宽度x4x8x16黑芯片数量1684上图是最常见的x8,有八颗黑芯片颗粒。x16的性能和x8相比如何?

更糟,因为x16的bankgroup更少。

DDR4 x8 4银行组

图片来自https://www . micron . com/-/media/client/global/documents/products/data-sheet/DRAM/DDR 4/8GB _ DDR 4 _ SDRAM.pdf。

DDR4 x16双排组

DDR银行等级

DDR的正面是一个等级,如果背面有颗粒就是另一个等级。物理贴图中的八个粒子形成一个等级。

其中一个粒子的结构图如上两张图所示,分为bankgroup和bankgroup。

每次我们发出一个读写命令,都是在操作的每个粒子中相同位置的银行。例如,芯片0的bank3、芯片1的bank3、芯片2的bank 3…

DDR银行集团

DDR的bankgroup可以理解为将粒子分成组进行运算,也可以抽象为将黑色粒子分成单个的小粒子,即每个bankgroup。

增加存储体的数量意味着可以增加存储体之间的流水线操作,因此存储体越多,吞吐量越大。

为什么会有银行集团?

要解决这个问题,首先要了解预取。

每一代新的DDR,外引脚pin的传输速度都翻倍。但实际上DDR内部真实内存的速度和延迟并没有改变,DDR是通过预取来完成这种错觉的。

DDR3 x8预取的本质;

X8表示每个粒子输出8位。DDR中的慢存储器可以一次输出64bit,在外部fast pin管脚上连续输出,可以得到8倍倍频。

如果xW W是每个粒子的位宽,DDR存储器和外部引脚的速度差是m,那么每个粒子预取WxN位。

在1 Gig x 8的图表中,右边的64是预取的64位。

DDR nddr DDR 2d dr 3d dr 4 DDR 5 preetch248816

预取8,总线宽度64Bit的DDR3带8个八度,正好对应64b。

如果16倍频程DDR4继续预取16,它将对应于128B,但不对应于64字节的cacheline。所以DDR4采用上述的bankgroup,在不同的Bank group之间切换输出,避免连续输出128Byte。

用32倍频程的DDR5 prefetch16,不会有输出128B的问题吗?

真的没有这个问题。如果要继续使用bankgroup方法,也很难在多个bank group之间切换。所以DDR5的64位总线砍了一半,32位x 16还是64B。

其实除了64bit还有ECC bit,只是我们不必了解。

DDR页面大小

DDR页面大小实际上是每次激活DDR时输出到行缓冲区的数据大小。具体计算方法是2 column _ width * chip _ width/8字节。

如果DDR的列地址是10位,则chip_width为4的页大小对应于512B,chip_width为8的页大小对应于1KB。

DDR行缓冲器

每次向DDR发送激活命令,都会有一整行DDR输出到行缓冲区,如上图所示。行缓冲器中当前请求的预取数据的一小部分被输出到外部。如果下次需要读另一行,需要先回写这一行,然后预充电位线,再开一行新的,还是挺贵的。

所以理想的情况是继续读取当前行的下一部分数据,这样就不需要回写,可以从行缓冲区连续读取。

图片来自https://ieeexplore.ieee.org/stamp/stamp.jsp? TP=ar number=6853217

在上图中,行大小,即页面大小是2KB。这一次,芯片3中的128b被预取。如果下一个128b能读,就发个command命令。

下面就拿这张图来回顾一下上面介绍的内容:

每个芯片都是16位宽,需要4个芯片组成64位。

外部时钟是800Mhz,因为DDR双倍速率传输,实际上是1600Mhz。内部时钟200Mhz,时钟差8倍。所以我们需要一次预取16x 8=128位。

注意,图中每个芯片都有一个红色条,即每次读取时,读取不同芯片相同位置的存储体。

那么为什么Chip3中不同银行的红条位置不同呢?

DDR存储体交错

同一存储体中不同行之间的DDR切换需要上述的恢复写回和预充电。

但是不同的存储体共用命令地址数据总线,但是内部存储器是独立的,所以我们可以先访问存储体0的第一行,存储体1的第七行,然后访问存储体3的第二行,存储体之间的流水线输出可以充分利用数据总线。

如下图所示,

DDR单元命令序列

上面说的DDR需要回写,因为DDR是电容组成的,存在漏电。除了回写,还需要定期刷新。上图中的Cs存储的是真实的内存。为简单起见,我们将电压理解为0/1 V。

图片来自https://ieeexplore.ieee.org/stamp/stamp.jsp? TP=ar number=7446096

在最后的操作之后,DRAM将被预充电,并且CBL将Cbl充电到0.5v的电势

如果我们发出读命令并激活,一条线将被激活,即WL线将被拉高。此时Cs的电位为0/1 V,CBL的电压为0.5 V,所以会发生电荷共享。

在感测阶段,电压差将通过感测放大器存储在行缓冲器中。

读命令将从行缓冲器预取相应长度的数据,并将其输出到外部。

读出放大器完成工作后,将Vdd的电压充到1V,恢复,此时损坏的数据将被恢复。

断开字线并将位线充电到0.5v,这是预充电操作。

简单地说

Activate激活对应的行字线,数据输出到行缓冲器。

读取列命令对应于从行缓冲器读取数据。

预充电命令将位线恢复到一半电压。

回顾唐子红