指导阅读

本文将简要介绍数字芯片设计的十个过程以及每个过程中使用的主流EDA软件。

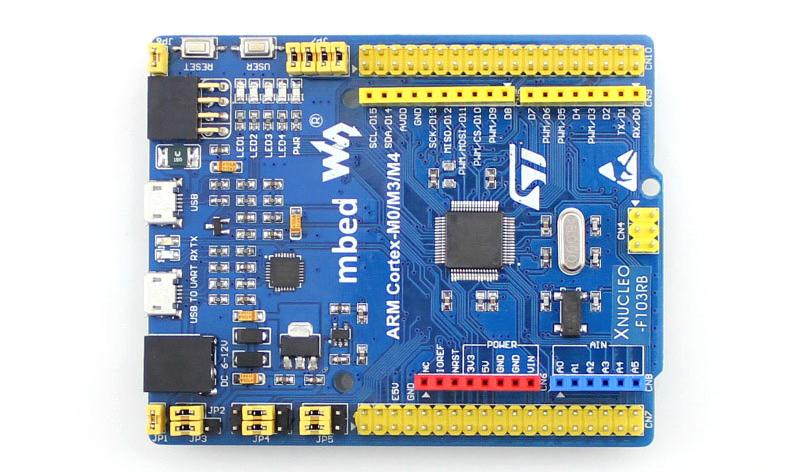

芯片在我们的生活和工作中无处不在。例如,交通智能卡内嵌有带微处理器、存储单元和芯片操作系统的芯片;手机主板上集成了上百个芯片,有的负责无线电收发,有的负责功率放大,有的负责存储照片和文件,处理音频,识别指纹、虹膜和人脸。当然手机最重要最贵的还是属于CPU,它是控制中心,是逻辑运算的中心,通过运行内存中的软件和数据库来控制手机。根据处理的信号类型,芯片可以分为数字芯片和模拟芯片。做芯片,首先要完成芯片设计。本文将简要介绍数字芯片设计的十个过程以及每个过程中使用的主流EDA软件。

芯片设计可以分为前端设计(逻辑设计)和后端设计(物理设计)。前端设计包括以下四个步骤:

前端设计

(1)算法或硬件架构的设计和分析

在明确了芯片的设计需求后,系统架构师会将这些市场需求转化为芯片的规格,形成芯片规格,即芯片的规格。本规范将详细描述芯片的功能、性能、尺寸、封装和应用。

系统架构师会根据芯片的特点,划分芯片内部的规格用途,规划各部分的功能需求空间,建立不同单元之间的连接方式,确定设计的总体方向。这一步在后续的设计中起着至关重要的作用。如果区域划分不够,这个区域的功能实现无法完成,就会导致之前的工作全部被推翻,重新开始。设计出来的就要制造出来,所以芯片设计需要和产业链后端晶圆的制造和封装测试环节紧密配合。工程师不仅需要考虑工艺能否实现相应的电路设计,还需要整合产业链资源,保证芯片产品的及时供应。编程语言(MATLAB,C,C,System C,System Verilog等。)将用于构建这里的算法。对于不同类型的芯片,工程师会有不同的偏好。

(2)RTL码的实现(寄存器传输级)

由于芯片设计的复杂性,设计师不是在晶体层面设计,而是在更高的抽象层面。RTL实现是根据第一步架构设计的结果,将其转换成Verilog HDL或VHDL语言。这两种语言是世界上最流行的两种硬件描述语言。它们是以文本形式描述数字系统硬件的结构和行为的硬件编程语言,可以用来表示逻辑输出,如逻辑电路图和表达式。所以可以理解为前一步是整体规划,第二步是具体实施。设计工程师通过逐行输入代码来实现电路的功能。输出被转换成Verilog HDL或VHDL语言。

(3)代码检查和分析

这一步是检查代码是否有错误,以保证代码不会出现歧义,导致实现结果与设计目的不一致。一般来说,最常用的代码检查工具是Synopsys的Spyglass。这个工具主要检查两个内容,一个是Lint检查,一个是CDC(时钟域交叉)检查。Lint检查不仅可以检测编译过程中的许多编译器错误,还可以关联许多文件进行错误检查和代码分析;CDC是电路设计中对同步电路设计的检验。在大规模电子电路设计中,设计人员很难将整个大规模同步电路设计出来,只能根据电路的逻辑功能将其分成若干个同步电路部分,由不同的时钟域控制。这些部分可能会重叠,会导致重叠部分的触发器状态变化在统一时钟的作用下无法完成,从而造成电路的亚稳态。亚稳态电路会使组合逻辑电路的输入状态未知,甚至引起su

望远镜截图,图片来自网络

(4)功能验证

这一步是验证芯片设计是否满足预定设计要求的关键步骤,主要是验证电路设计的逻辑功能的正确性,而不是电路的物理特性(后面的步骤会讲到物理验证)。数字仿真器是验证数字集成电路逻辑功能的主要手段。

随着超大规模集成电路的快速发展,高性能数字仿真器已经成为数字集成电路设计和验证中必不可少的一部分。近年来,数字模拟器技术发展迅速,如今的主流数字仿真软件可以支持具有数十亿晶体管的VLSI的逻辑功能,进行高效准确的仿真验证。为了保证芯片的稳定性,这个阶段会持续几个月。工程师常用的EDA工具有Mentor(西门子EDA)的Modelsim、Synopsys的VCS和Candence的NC-Verilog。

功能模拟验证

在整个芯片设计过程中的位置(粗体)

后端设计

(5)逻辑综合

从这一步开始,我们将进入芯片设计的后端设计(物理设计)阶段。主要负责将RTL码转换成网表(Netlist,包含RTL所有的逻辑信息,以及离散傅立叶变换、时钟门控和I/O等。)在实际后端使用。网络的好坏对芯片的布局起着决定性的作用。在这个过程中,要考虑工艺的电气、物理特性等因素,尽可能做到性能、功耗、面积的PPA优化。合成的质量在一定程度上取决于合成软件的性能。业界流行的两个逻辑综合工具是Synopsys的Design Compiler和Genus of Cadence。对合成工程师的一个基本要求是熟练掌握这两个工具的用法。

(6)布局和布线(PD)

布局是数字后端最重要的工作,主要是将网表转换成GDSII流格式(这是集成电路布局数据转换的标准数据文件格式,包含集成电路布局中平面的几何形状、文本或标签,由层次结构组成),确定各种功能电路的布局位置。产品开发的步骤包括平面布置、布局、CTS、优化、布线和ECO等。以确保每个模块满足时序和物理制造的要求。这一步是后端设计中的核心工作。布局高度依赖工具,工具的操作相对复杂。业界常用的有Cadence的Innovus和Synopsys的ICC。

国内外排版工具制造商

Leplace图形界面

(7)静态时间序列分析

STA(静态时序分析)是芯片后端设计的重要步骤。芯片上有大量极其微小的金属元件。这些元件大小不同,通过导线流经这些元件的时间延迟也会不同。因为元器件太小,芯片的布局肯定会受到这些大小不一的元器件以及它们之间引线的制约。静态时序分析是模拟各种组件的互联和不同的情况,找出存在的问题。

静态分析需要保证芯片设计中的所有路径,满足内部时序单元对建立时间和保持时间的设计要求。也就是说,无论信号的起点是什么,信号都可以及时传输到路径的终点。同时还应满足电平跳变时间、电容、噪声等要求。STA需要制定整个芯片的时序约束文件,选择芯片需要签收的角落(工作范围)和整个芯片的时序ECO流程,难度很大。STA广泛应用于Synopsys Primetime和Cadence Tempus软件中。值得一提的是,国内洪欣微纳的ChimeTime是一款静态定时签收工具,提供SPICE模拟精度的签收结果。

(8)实物验证

实物验证也是生产前(即试生产)的重要事项。如果物理验证错误,芯片生产将失败。在布局工具中,真正的物理验证需要检查器件的底层。因此,物理验证需要将金属层和底层金属结合在一起,对整个芯片进行DRC(设计规则检查)。同时需要做整个芯片的LVS(版图和原理图一致性检查)和ERC(电学规则检查),确保芯片不违反任何物理设计规则。物理验证的主要工具是在Mentor(西门子EDA)的Calibre中进行的,这也是业界标准的物理验证工具。

(9)功耗分析(PA)

功耗分析也是芯片发行的重要步骤。功耗分析的两个主要任务是IR压降(电压降)和EM(电迁移)。及时将结果反馈给布局任务组,以便他们及时修改后端设计图纸,解决设计中的潜在问题。功耗分析常用的软件有Ansys的Redhawk,Cadence的Voltus,Synopsys的Ptpx。

(10)时序模拟

这一步是模拟芯片的实际工作状态,也就是后仿真,验证功能是否正常。时序仿真使用布局后器件给出的模块和连接的延迟信息,评估电路在最坏情况下的行为。用于时序模拟的模拟器与上述第四步中用于功能模拟的模拟器相同。不同的是在接线前进行功能仿真,只关注输出和输入的逻辑关系是否正确,不考虑延时信息;布线后进行时序模拟,不仅关注输出与输入的逻辑关系是否正确,还计算延时信息。

综上所述,数字芯片的前端设计就是逻辑设计,通过逻辑电路实现预期的功能。后端部分是前端设计的物理实现。芯片设计完成后,Fabless公司一般会将设计结果的GDSII格式记录的电路版图数据交给Foundry进行流片,即试产。为什么叫流片?因为在七八十年代,芯片的设计数据是写在磁带或胶片上,送到工厂的。设计团队将数据写入磁带,称为磁带输入,工厂从磁带读取数据,称为磁带输出。虽然随着科技的发展,自动化集成电路版图工具软件早已取代了磁带,但这个术语一直在使用。流片完成后,就可以生产芯片了。由于芯片流的巨大成本,需要在设计阶段尽可能保证芯片的可靠性和可制造性。主流EDA软件的验证和仿真功能比较完善,通过各个阶段的不断验证和仿真,可以减少芯片中的错误,降低芯片的成本,保证芯片的可靠性。芯片设计非常专业,每个设计阶段涉及的软件种类非常多。虽然全球EDA软件市场只有数百亿美元,但它撬动了万亿美元的集成电路市场。因此,EDA软件产业具有重要的战略意义。目前,我国高度重视工业软件的高速发展,国产EDA软件迎来了发展的春天。中国EDA市场正在全力以赴,出现了华大九天、古伦电子、广利威、九通方、上海立信、新爪掌、新芯视界、洪欣微纳等知名品牌。虽然卡脖子EDA领域的问题对我国高端芯片的设计和制造产生了很大的影响,也给国内EDA软件厂商带来了更大的市场机遇。通过更多芯片设计、制造、封装、测试企业在实践中的应用,不断反馈对国产EDA软件的应用需求和软件改进需求,快速提升我国EDA软件的技术水平。

审计刘清