本文为大家带来五人表决器的五种电路设计方案。

五人表决器电路设计方案一:基于74LS151的五人表决器电路系统原理。只要赞成人数大于等于三,五人投票器就投票。所以只需要把每个投票人的结果加起来,判断结果值就可以了。设五个开关A、B、C、D、E为表决器的五个输入变量。当输入变量为逻辑“1”时,表示表决器“赞成”,红灯亮;当输入变量为“0”时,表示投票人“不赞成”,红灯不亮;当输出逻辑“1”时,表示表决“通过”,绿灯亮;当输出逻辑“0”时,表示表决“未通过”,绿灯不亮;当表决器的五个输入变量中有三个以上(含三个)为“1”时,表决器的输出为“1”,绿灯亮。

真值表

如果绿灯亮,表示表决通过;如果绿灯不亮,说明没有通过。

电路设计

原理图五人表决器电路设计方案二:verilog五人表决器编程模块vote5(a,B,C,D,E,F);

输入a,b,c,d,e;

产出f;reg f;

reg[2:0]count 1;

初始count 1=0;

总是@(a,b,c,d,e)

开始

count 1"=a b c d e;

f=count1《3?0:1;

结束

末端模块

测试程序模块测试;

reg a;

reg b;

reg c;

reg d;

reg e;

电线f;

vote5 uut(。答(答)、乙(乙)。c(c)。d(d)。e(英)、f(f));

初始开始

a=0;

b=0;

c=0;

d=0;

e=0;

#100

a=1;

b=0;

c=0;

d=0;

e=0;

#100

a=1;

b=1;

c=0;

d=0;

e=0;

#100

a=1;

b=1;

c=1;

d=0;

e=0;

#100

a=1;

b=1;

c=1;

d=1;

e=0;

#100

a=1;

b=1;

c=1;

d=1;

e=1;

结束

末端模块

模拟图

五人表决器电路设计方案三:用VHDL编程的五人表决器,利用实验平台的LED发光阵列实现投票结果和每个人的投票信号。LED1需要显示认可信号(led_agr)和不认可信号(led_opp)。LED3、LED4、LED5也显示判断结束信号。led10、 led 11、 led 12、 led 13、 led 14显示五个人的投票信号。

系统启动时,数码管5、6分别显示“FF”字样,使用的数码管全部关闭,投票开始。此时,用户可以通过拨动开关输入五个人的投票意见,并分别通过LED 10 ~ LED 14显示。当用户按下锁定按钮(键6)时,LED 10 ~ LED 14的状态被锁定。LED3、LED4、LED5同时亮起。此时,无论如何输入投票意见,LED10 ~ LED 14的状态都不会改变。同时系统会计算赞成人数和反对人数,用数码管显示5、6,系统会计算赞成人数和反对人数的大小关系,并通过LED 1和LED8,判断反对:LED8开启)。此时,在用户按下清除键clr(键7)之后,系统返回到新启动的状态。

源代码

模拟图

五人表决器电路设计方案四:基于74HC138的五人表决器对于五人表决器,首先设五人为A B C D E,Y为投票结果。如果有三个以上的人同意(同意“1”,不同意“0”),红灯亮(红灯为“1”),绿灯亮(绿灯为“0”)。如果红灯亮,表示表决通过;如果绿灯亮了,说明没有通过。

布图设计

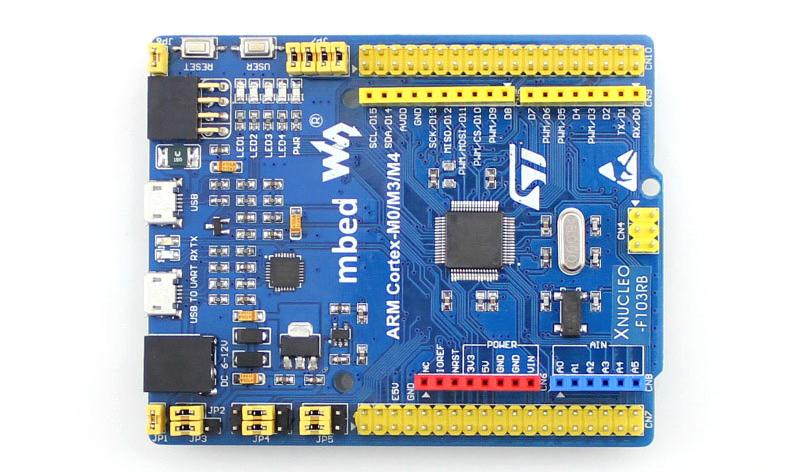

五人表决器电路设计方案五:基于FPGA的五人表决器电路原理图

该电路图可以实现表决器的控制和显示。键8到2是五个表决器,分别是复位和开始键。通过数码管显示投票人数和剩余时间。二极管D8显示通过和失败。

销锁定

当模拟处于重置状态时,外部输入对结果没有影响。所以时间还是10秒,输出统计数是0。仿真波形如下图所示。

复位时的仿真结果

在非复位状态下,主机按下开始键。投票开始。没有人投票。时间变成0。投票结束了。仿真波形如下图所示。

没人同意时的模拟结果。

在非复位状态下,主机按下开始键。投票开始。超过投票时间,投票无效。仿真波形如下图所示。

指定时间之外的模拟结果

在非复位状态下,主机按下开始键。投票开始。规定时间内只有两个人同意。仿真波形如下图所示。

两个人意见一致时的结果。

在非复位状态下,主机按下开始键。投票开始。规定时间内只有三个人同意。仿真波形如下图所示。

结果当三个人都同意的时候。

在非复位状态下,主机按下开始键。投票开始。规定时间内只有四个人同意。仿真波形如下图所示。

结果当四个人意见一致时。

在非复位状态下,主机按下开始键。投票开始。规定时间内只有五个人同意。仿真波形如下图所示。

结果当五个人都同意的时候。