为什么启动ARM有两种方式?ARM7和ARM-Cortex有什么区别?快速中断和中断呢?

为什么ARM (NAND FLASH)有两种启动模式。也不闪)?

这主要是由两种闪光灯的不同特性决定的。

NAND FLASH容量大,存储单位位数据的成本低很多。但是NAND FLASH要按照特定的时序读写,所以CPU不能直接寻址NAND FLASH中的数据。CPU通过专门的nand flash控制器读写NAND FLASH中的数据,所以NAND FLASH更适合存储数据。

NOR FLASH容量小,速度快。读写NOR FLASH时,通过输入地址,然后给出读写信号,就可以从数据总线上获取数据,但价格比NAND FLASH高,所以适合做程序存储器。

综上所述,NOR FLASH可以直接连接到arm的总线上,但是DAND FLASH需要通过NAND FLASH控制器连接到S3S2440上。

ARM7和ARM-Cortex的区别

ARM7:ARMv4架构,ARM9:ARMv5架构,ARM11:ARMv6架构,ARM-Cortex系列:ARMv7架构。

ARM7没有MMU(内存管理单元),只能叫MCU(微控制器)。它无法运行Linux、WinCE等现代多用户多进程操作系统,因为它需要MMU来运行这些系统,这样每个用户进程才能被分配到自己独立的地址空间。UcOS,ucLinux,这些精简的实时RTOS不需要MMU,当然可以在ARM7上运行。

ARM9、ARM11是带MMU的嵌入式CPU(处理器),可以运行Linux等多用户多进程操作系统,应用场合与ARM7不同。

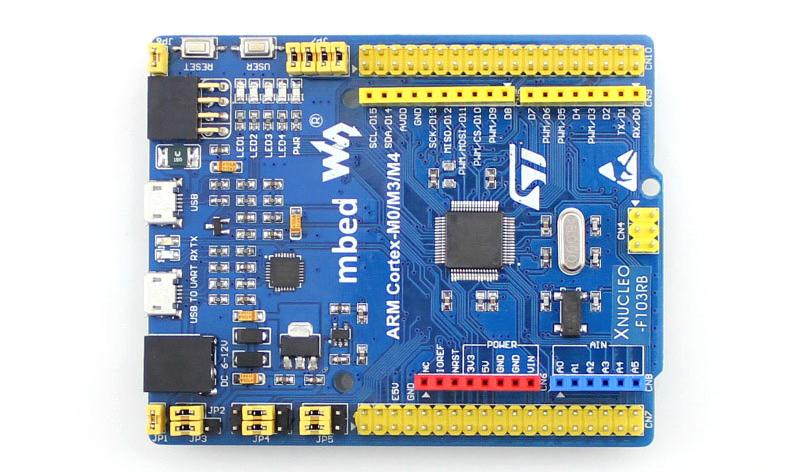

到了ARMv7架构,开始以Cortex命名,分为Cortex-A、Cortex-R、Cortex-M三个系列,三个系列分工明确:“A”系列面向基于虚拟内存的前沿操作系统和用户应用;“R”系列针对实时系统;“M”系列双微控制器。简单来说,Cortex-A系列是用于移动领域的CPU,Cortex-R和Cortex-M系列是用于实时控制领域的MCU。

所以看起来ARM7和Cortex-M很像,因为都是MCU,但是是不同代的MCU,架构不同(Cortex-M比ARM7高三代!),所以性能上也有很大差距。此外,Cortex-M系列细分为超低功耗的M0、M3、M4和M0。用户根据成本、性能、功耗等因素选择芯片。

我相信你现在已经知道ARM7、Cortex-M的区别了,但是边肖还是花了一些时间在这里整理了一下,可以帮助后来的初学者理解这些基本的概念问题。

ARM的FIQ(快速中断)IRQ(中断)

IRQ,FIQ的定义:这是一个普通的中断。当我们的程序定义了这个中断,并且在程序运行过程中发生IRQ中断时,芯片会如下操作:中断处理器,使用IRQ请求线加速ARM,ARM会知道有IRQ中断到来,然后切换到IRQ模式。同样,如果中断设置为FIQ,当中断发生时,中断处理程序通过FIQ请求线告诉ARM,ARM知道有FIQ中断到来,然后切换到FIQ模式。

那么问题来了,为什么会有这两个中断,或者说为什么会分成这两个中断?原因很简单,速度不同,FIQ的意思是中断速度快,那么问题又来了,FIQ为什么快?

原因:

1.arm的FIQ模式提供更多的分组寄存器,r8至r14和SPSR,但在IRQ模式下没有这么多,并且没有对应于R8、R9、R10、R11和R12的分组寄存器,这意味着在ARM的IRQ模式下,中断处理程序必须保存R8至R12寄存器,然后程序必须在退出中断处理时恢复这些寄存器。在FIQ模式下,由于这些寄存器都有分组寄存器,因此CPU在切换模式时会自动将这些值保存到分组寄存器中,并在退出FIQ模式时自动恢复这些值,因此FIQ的处理速度比IRQ快。不要小看这些寄存器。ARM编译时,如果你的FIQ中断处理程序使用了足够多的独立寄存器来操作,就不会堆栈通用寄存器,这样也节省了一些时间。

2.FIQ的优先级高于IRQ。如果FIQ和IRQ同时产生,那么FIQ将首先被处理。

3.在symbian系统中,当CPU处于FIQ模式处理FIQ中断时,预取指令异常,未定义指令异常,所有软件中断被禁止,所有中断被屏蔽。所以FIQ会快速执行,不会被其他异常或中断中断,所以比IRQ快。而IRQ就不同了。ARM处理IRQ模式处理IRQ中断时,如果一个FIQ中断请求来了,正在执行的IRQ中断处理程序就会被抢走,ARM切换到FIQ模式执行这个FIQ,所以FIQ比IRQ快很多。

4:另外,FIQ的入口地址是0x1C,IRQ的入口地址是0x18。每个写过完整汇编系统的人都明白其中的区别。18中只能放一条指令,这个地方为了不与1C中的FIQ冲突只能跳转。与FIQ不同,1C之后没有中断向量表,所以FIQ的中断处理程序可以直接放在1C中。由于跳转范围的限制,至少缺少一条跳转指令。